### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **FEATURES AND BENEFITS**

- · Automotive AEC-Q100 qualified

- Enhanced fault handling for ASIL B system compliance

- Wide input voltage range of 4.5 to 40 V for start/stop, cold crank, and load dump requirements

- Operate in Boost or SEPIC mode for flexible output

- Gate driver for external MOSFET to deliver higher output power

- Six integrated LED current sinks, up to 140 mA each

- Boost switching frequency synced externally or programmed from 260 kHz to 2.3 MHz

- · Programmable boost frequency dithering to reduce EMI

- Advanced control allows minimum PWM on-time down to 0.3 µs, and avoids MLCC audible noises

- LED contrast ratio: 15,000:1 at 200 Hz using PWM dimming alone, 150,000:1 when combining PWM and analog dimming

- Excellent input voltage transient response even at lowest PWM duty cycle

- Gate driver for optional P-channel MOSFET input disconnect switch

- · Extensive fault protection features

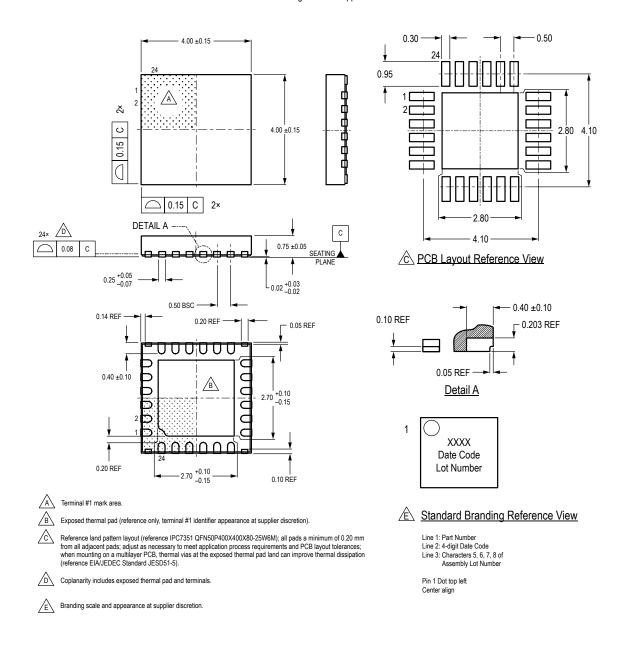

#### **PACKAGE:**

24-Pin 4 mm × 4 mm QFN with Wettable Flank

Not to scale

#### **DESCRIPTION**

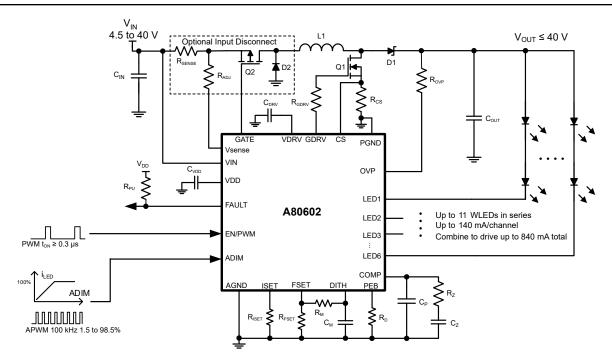

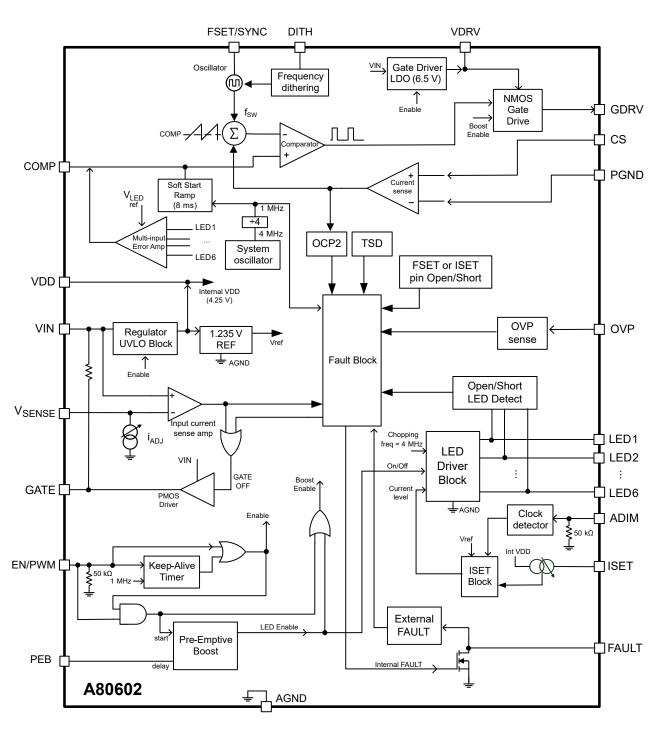

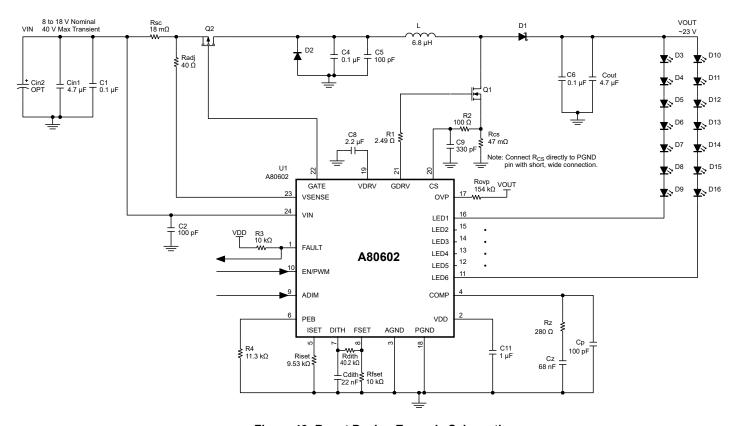

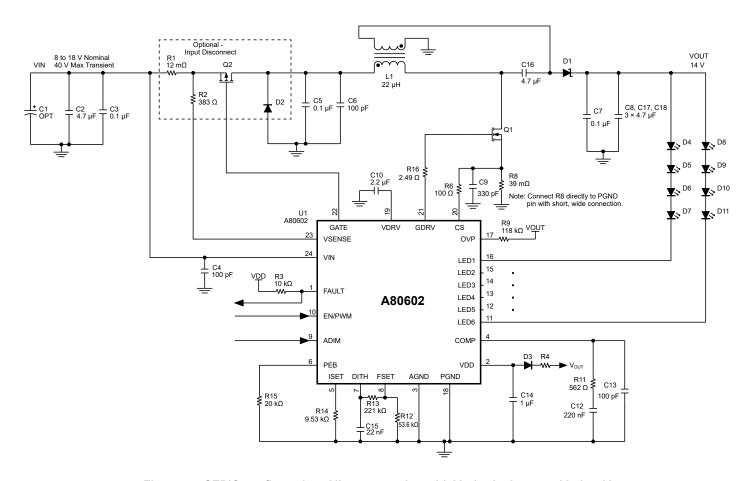

The A80602 is a multi-output LED driver for automotive applications such as exterior lighting, heads-up display, and midsize LCD backlighting. It implements a current-mode boost/SEPIC converter with gate driver for external N-MOSFET.

The A80602 provides six integrated current sinks driving up to 140 mA per string. Multiple sinks can be paralleled together to achieve higher LED currents up to 840 mA. The IC operates from a single power supply from 4.5 to 40 V; once started, it can continue to operate down to 4 V. This allows it to withstand stop/start, cold crank, and load dump conditions encountered in automotive systems.

The A80602 can control LED brightness through an external PWM signal. By using the patented Pre-Emptive Boost control, an LED brightness contrast ratio of 15,000:1 can be achieved using PWM dimming at 200 Hz. A higher ratio of 150,000:1 is possible when using a combination of PWM and analog dimming.

Continued on next page...

#### **APPLICATIONS**

- Automotive infotainment backlighting

- Automotive heads-up display

- Automotive interior and exterior lighting

Figure 1: A80602 Simplified Circuit Configuration

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **DESCRIPTION** (continued)

Switching frequency can be externally synchronized or programmed between 260 kHz and 2.3 MHz. This allows operation either above or below the AM band. A programmable dithering feature further reduces EMI.

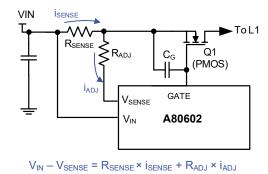

The A80602 provides protection against output short, overvoltage, open- or shorted-LED pin, and overtemperature. A cycle-by-cycle current limit protects the external boost switch against high current overloads. An external P-channel MOSFET can optionally be used to disconnect input supply in case of output to ground short fault. The A80602-1 is similar to A80602 except it adopts 'One-Out-All-Out' fault handling (See Fault Table section for details).

#### **SELECTION GUIDE** [1]

| Part Number    | Fault Handling   | LED Driver | Package                                       | Packing              |

|----------------|------------------|------------|-----------------------------------------------|----------------------|

| A80602KESJSR   | One-Out-Continue | 6 × 140 mA | 24-pin 4 × 4 mm wettable flank QFN            | 6000 piagos por rool |

| A80602KESJSR-1 | One-Out-All-Out  | 0 ^ 140 MA | with exposed thermal pad and sidewall plating | 6000 pieces per reel |

<sup>[1]</sup> Contact Allegro for additional packing options.

#### ABSOLUTE MAXIMUM RATINGS [2]

| Characteristic                                           | Symbol                                    | Notes                                                                  | Rating                                                                   | Unit |

|----------------------------------------------------------|-------------------------------------------|------------------------------------------------------------------------|--------------------------------------------------------------------------|------|

| LEDx Pin                                                 | V <sub>LEDx</sub>                         | x = 16                                                                 | -0.3 to 40                                                               | V    |

| OVP pin                                                  | V <sub>OVP</sub>                          |                                                                        | -0.3 to 40                                                               | V    |

| VIN                                                      | V <sub>IN</sub>                           |                                                                        | -0.3 to 40                                                               | V    |

| VSENSE, GATE                                             | V <sub>SENSE</sub> ,<br>V <sub>GATE</sub> |                                                                        | Higher of –0.3<br>and (V <sub>IN</sub> – 7.4) to<br>V <sub>IN</sub> +0.4 | ٧    |

| VDRV, GDRV                                               | V <sub>DRV,</sub> V <sub>GDRV</sub>       |                                                                        | -1.0 to 7.5                                                              | V    |

| CS                                                       | V <sub>CS</sub>                           |                                                                        | -0.3 to 7                                                                | V    |

| EN/PWM, FAULT, ADIM, COMP,<br>DITH, PEB, FSET, ISET, VDD |                                           | External input signals must not be higher than V <sub>IN</sub> + 0.4 V | -0.3 to 5.5                                                              | V    |

| Operating Ambient Temperature                            | T <sub>A</sub>                            | Range K                                                                | -40 to 125                                                               | °C   |

| Maximum Junction Temperature                             | T <sub>J(max)</sub>                       |                                                                        | 150                                                                      | °C   |

| Storage Temperature                                      | T <sub>stg</sub>                          |                                                                        | -55 to 150                                                               | °C   |

<sup>[2]</sup> Stresses beyond those listed in this table may cause permanent damage to the device. The absolute maximum ratings are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the Electrical Characteristics table is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### THERMAL CHARACTERISTICS: May require derating at maximum conditions; see application information

| Characteristic             | Symbol          | Test Conditions [4]                                        |    | Unit |

|----------------------------|-----------------|------------------------------------------------------------|----|------|

| Package Thermal Resistance | $R_{\theta JA}$ | ES package measured on 4-layer PCB based on JEDEC standard | 37 | °C/W |

<sup>[4]</sup> Additional thermal information available on the Allegro website.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **Table of Contents**

| Features and Benefits                  | 1  |

|----------------------------------------|----|

| Description                            | 1  |

| Applications                           |    |

| Package                                | 1  |

| Selection Guide                        | 2  |

| Absolute Maximum Ratings               | 2  |

| Thermal Characteristics                |    |

| Functional Block Diagram               | 4  |

| Pinout Diagram and Terminal List       | 5  |

| Electrical Characteristics             |    |

| Functional Description                 | 9  |

| Enabling the IC                        | 9  |

| Powering Up: LED Detection Phase       | 10 |

| Powering Up: Boost Output Undervoltage | 12 |

| Soft Start Function                    | 12 |

| Frequency Selection                    | 13 |

| Synchronization                        | 13 |

| Loss of External Sync Signal           | 14 |

| LED Current Setting                    | 15 |

| PWM Dimming                            | 15 |

| Switching Frequency Dithering          | 16 |

| Dro Emptive Report (DER)               | 17 |

| Analog Dimming                                     | 18 |

|----------------------------------------------------|----|

| ADIM Mode                                          | 18 |

| APWM Mode                                          | 19 |

| Extending LED Dimming Ratio                        | 20 |

| Analog Dimming with External Voltage               | 21 |

| VDD                                                | 22 |

| VDRV                                               | 22 |

| Shutdown                                           | 22 |

| Fault Detection and Protection                     | 23 |

| FAULT Status                                       | 23 |

| LED String Partial-Short Detect                    | 25 |

| Overvoltage Protection                             | 26 |

| Boost Switch Overcurrent Protection                | 27 |

| Input Overcurrent Protection and Disconnect Switch | 28 |

| Setting the Input Current Sense Resistor           |    |

| Input UVLO                                         | 29 |

| Fault Protection During Operation                  | 29 |

| Package Outline Drawing                            | 32 |

| Appendix A: Design Example                         | 33 |

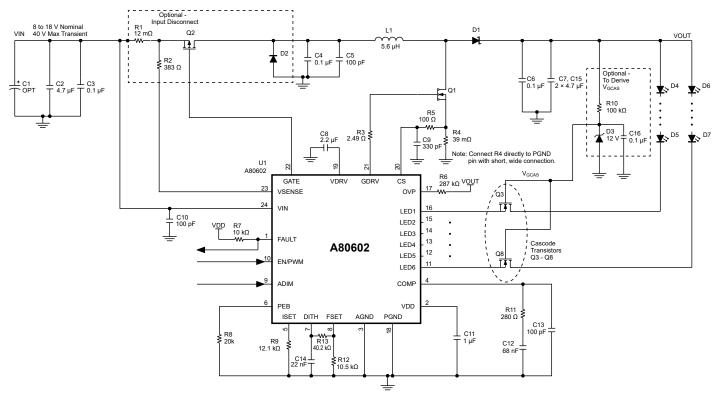

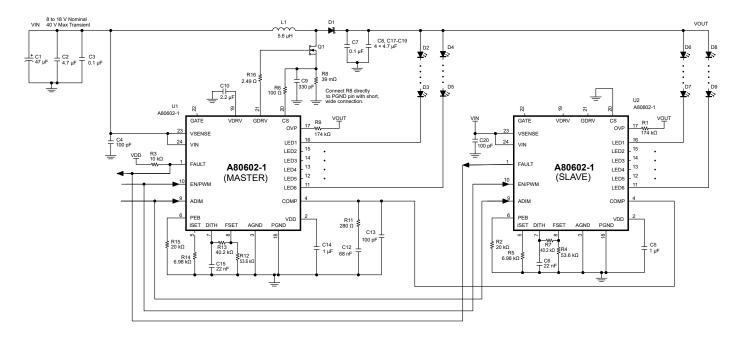

| Appendix B: Reference Designs                      | 38 |

| Appendix C: External MOSFET Selection Guide        | 44 |

Figure 2: Functional Block Diagram

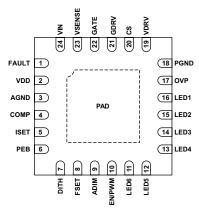

#### PINOUT DIAGRAM AND TERMINAL LIST

Package ES, 24-Pin QFN Pinouts

#### **Terminal List Table**

| Number | Name     | Function                                                                                                                                                                                                                                                                                                                                      |

|--------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | FAULT    | This pin is an open drain type configuration that is pulled low when a fault occurs. Connect a pull-up resistor between this pin and desired logic level voltage.                                                                                                                                                                             |

| 2      | VDD      | Output of internal LDO (bias regulator). Connect a 1 µF decoupling capacitor between this pin and AGND. V <sub>DD</sub> is regulated at ~4.25 V.                                                                                                                                                                                              |

| 3      | AGND     | LED current Ground. Also serves as 'quiet' ground for analog signals.                                                                                                                                                                                                                                                                         |

| 4      | COMP     | Output of the error amplifier and compensation node. Connect a series RC network from this pin to AGND for control loop compensation.                                                                                                                                                                                                         |

| 5      | ISET     | Connect R <sub>ISET</sub> resistor between this pin and AGND to set the 100% LED current.                                                                                                                                                                                                                                                     |

| 6      | PEB      | Pre-Emptive Boost control: Connect resistor from PEB pin to AGND to fine-tune the delay between boost switch and LED current sinks. Leave pin open for minimum PEB delay of 1 μs.                                                                                                                                                             |

| 7      | DITH     | Dithering control: connect a capacitor to AGND to set the dithering modulation frequency (1 to 22 kHz). Connect a resistor between DITH and FSET pins to set the dithering range (such as ±5% of f <sub>SW</sub> ).                                                                                                                           |

| 8      | FSET     | Frequency/synchronization pin. A resistor RFSET from this pin to AGND sets the switching frequency f <sub>SW</sub> (with dithering superimposed) between 200 kHz and 2.3 MHz. It can also be used to synchronize f <sub>SW</sub> to an external frequency between 260 kHz and 2.3 MHz (frequency dithering is disabled in this case).         |

| 9      | ADIM     | Analog dimming. Apply a PWM clock (40 to 1000 kHz) to pin and the duty cycle of this clock determines the LED current. Alternatively, apply DC level between 0.2 and 2 V to vary LED current between 10% and 100%. If unused, pull pin above 2 V for 100%.                                                                                    |

| 10     | EN/PWM   | Enables the IC when this pin is pulled high. It also controls the on/off state of LED current sinks to reduce the light intensity by using pulse width modulation. Typical PWM dimming frequency is in the range of 200 Hz to 2 kHz. When this pin is pulled low, the IC remains in standby mode for up to 16 ms, then shuts down completely. |

| 11-16  | LED6LED1 | LED current sinks #6 to #1. Connect the cathode of each LED string to pin. Unused LED pin must be terminated to AGND through a resistor (4.75 kΩ for LED1/3/4/5, 2.37 kΩ for LED2/6).                                                                                                                                                         |

| 17     | OVP      | Overvoltage Protection. Connect external resistor from VOUT to this pin to adjust the over voltage protection threshold.                                                                                                                                                                                                                      |

| 18     | PGND     | Power Ground for internal Gate Driver. Connect pin to external power GND with shortest path.                                                                                                                                                                                                                                                  |

| 19     | VDRV     | Gate driver supply voltage (~6.5 V). Connect a 2.2 μF MLCC to PGND for buffer.                                                                                                                                                                                                                                                                |

| 20     | cs       | Current Sense for peak current control of power switch. Connect to sense resistor at the Source terminal of external power MOSFET.                                                                                                                                                                                                            |

| 21     | GDRV     | Gate driver for power switch. Connect to Gate of external power MOSFET. (External FET must be fully enhanced at V <sub>GS</sub> = 5 V).                                                                                                                                                                                                       |

| 22     | GATE     | Output gate driver pin for external P-channel MOSFET (input disconnect switch).                                                                                                                                                                                                                                                               |

| 23     | VSENSE   | Connect this pin to the negative sense side of the input current sense resistor Rsc. The threshold voltage is measured as V <sub>IN</sub> – V <sub>SENSE</sub> . There is also fixed i <sub>ADJ</sub> current sink to allow for trip threshold adjustment.                                                                                    |

| 24     | VIN      | Input power to the IC as well as the positive side of input current sense resistor.                                                                                                                                                                                                                                                           |

| -      | PAD      | Exposed pad of the package providing enhanced thermal dissipation. Must be connected to the ground plane(s) of the PCB with at least 8 vias, directly in the pad.                                                                                                                                                                             |

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

ELECTRICAL CHARACTERISTICS [1]: Unless otherwise noted, specifications are valid at  $V_{IN}$  = 12 V,  $T_J$  = 25°C, • indicates specifications guaranteed over the full operating temperature range with  $T_J$  = -40°C to 125°C, typical specifications are at  $T_J$  = 25°C

| Characteristics                    | Symbol                                     | Test Conditions                                                                      |    | Min. | Тур. | Max. | Unit |

|------------------------------------|--------------------------------------------|--------------------------------------------------------------------------------------|----|------|------|------|------|

| INPUT VOLTAGE SPECIFICATIONS       |                                            |                                                                                      |    |      |      |      |      |

| Operating Input Voltage Range [3]  | V <sub>IN</sub>                            |                                                                                      | •  | 4.5  | -    | 40   | V    |

| VIN UVLO Start Threshold           | V <sub>UVLO(rise)</sub>                    | V <sub>IN</sub> rising                                                               | •  | -    | -    | 4.45 | V    |

| VIN UVLO Stop Threshold            | V <sub>UVLO(fall)</sub>                    | V <sub>IN</sub> falling                                                              | •  | -    | _    | 4.05 | V    |

| UVLO Hysteresis [2]                | V <sub>UVLO_HYS</sub>                      |                                                                                      |    | 300  | 400  | 500  | mV   |

| INPUT CURRENTS                     |                                            |                                                                                      |    |      |      |      |      |

| VIN Pin Operating Current          | I <sub>OP</sub>                            | EN and PWM = H, C <sub>GATE</sub> = 1 nF from GDRV to PGND, f <sub>SW</sub> = 2 MHz  | •  | -    | 22   | 32   | mA   |

| VIN Pin Sleep Current              | I <sub>SLEEP</sub>                         | V <sub>IN</sub> = 16 V, V <sub>EN</sub> / V <sub>PWM</sub> = V <sub>SYNC</sub> = 0 V | •  | -    | 1    | 5    | μΑ   |

| INPUT LOGIC LEVELS (EN/PWM,        | ADIM)                                      |                                                                                      |    |      | -    |      |      |

| Input Logic Level-Low              | V <sub>IL</sub>                            |                                                                                      | •  | -    | -    | 0.4  | V    |

| Input Logic Level-High             | V <sub>IH</sub>                            |                                                                                      | •  | 1.5  | -    | -    | V    |

| Input Pull-Down Resistor           | R <sub>EN/PWM</sub> ,<br>R <sub>ADIM</sub> | Input = 5 V                                                                          |    | 30   | 50   | 70   | kΩ   |

| ANALOG DIMMING (ADIM)              | ·                                          |                                                                                      |    |      |      |      |      |

| Analog Dimming Current Level       | i <sub>ADIM50</sub>                        | DC 1.0 V applied to ADIM pin                                                         |    | -    | 50   | -    | %    |

| (shown as % of full-scale current) | i <sub>ADIM25</sub>                        | DC 0.5 V applied to ADIM pin                                                         |    | 23   | 25   | 27   | %    |

| APWM Frequency Range [2]           | f <sub>APWM</sub>                          | Clock signal applied to ADIM pin                                                     | •  | 40   | _    | 1000 | kHz  |

| APWM Duty Cycle Range [2]          | D <sub>APWM</sub>                          | f <sub>APWM</sub> = 100 kHz                                                          | •  | 1.5  | _    | 98.5 | %    |

| VDD REGULATOR                      |                                            |                                                                                      |    |      |      |      |      |

| Regulator Output Voltage           | V <sub>DD</sub>                            | V <sub>IN</sub> > 6 V, i <sub>LOAD</sub> < 1 mA                                      |    | 4.05 | 4.25 | 4.45 | V    |

| VDD UVLO Start Threshold           | V <sub>DDUVLOrise</sub>                    | V <sub>DD</sub> rising, no external load                                             |    | -    | 3.2  | _    | V    |

| VDD UVLO Stop Threshold            | V <sub>DDUVLOfall</sub>                    | V <sub>DD</sub> falling, no external load                                            |    | -    | 2.65 | -    | V    |

| ERROR AMPLIFIER                    |                                            |                                                                                      |    |      |      |      |      |

| Amplifier Gain [2]                 | gm                                         | V <sub>COMP</sub> = 1.5 V                                                            |    | -    | 900  | _    | μA/V |

| Source Current                     |                                            | V <sub>COMP</sub> = 1.5 V, A80602 (symm COMP)                                        |    | -    | -500 | _    | μΑ   |

| Source Guiterit                    | I <sub>EA(SRC)</sub>                       | V <sub>COMP</sub> = 1.5 V, A80602-1 (asymm COMP)                                     |    | -    | -700 | _    | μΑ   |

| Sink Current                       | I <sub>EA(SINK)</sub>                      | V <sub>COMP</sub> = 1.5 V                                                            |    | -    | +500 | -    | μΑ   |

| COMP Pin Pull Down Resistance      | R <sub>COMP</sub>                          | FAULT = 0, V <sub>COMP</sub> = 1.5 V                                                 | ot | -    | 1.4  | _    | kΩ   |

Continued on the next page...

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

ELECTRICAL CHARACTERISTICS [1] (continued): Unless otherwise noted, specifications are valid at  $V_{IN}$  = 12 V,  $T_J$  = 25°C, • indicates specifications guaranteed over the full operating temperature range with  $T_J$  = -40°C to 125°C, typical specifications are at  $T_J$  = 25°C

| Characteristics                                    | Symbol                               | Test Conditions                                                                                        |   | Min. | Тур.  | Max. | Unit  |

|----------------------------------------------------|--------------------------------------|--------------------------------------------------------------------------------------------------------|---|------|-------|------|-------|

| OVERVOLTAGE PROTECTION                             |                                      |                                                                                                        |   |      |       |      |       |

| OVP Pin Voltage Threshold                          | V <sub>OVP(th)</sub>                 | OVP pin connected to V <sub>OUT</sub>                                                                  | • | 2.2  | 2.5   | 2.8  | V     |

| OV/D Dire Comment Through ald                      |                                      | Current into OVP pin at 125°C                                                                          |   | 140  | 146.5 | 153  | μA    |

| OVP Pin Sense Current Threshold                    | I <sub>OVP(th)</sub>                 | Measured over temperature                                                                              | • | 140  | 150   | 160  | μA    |

| OVP Sense Current Temperature<br>Coefficient [2]   | Δi <sub>OVP</sub>                    | Current into OVP pin                                                                                   |   | -    | -36   | -    | nA/°C |

| OVP Pin Leakage Current                            | I <sub>OVPLKG</sub>                  | V <sub>OUT</sub> = 16 V, EN = L                                                                        | • | -    | 0.1   | 1    | μA    |

| OVB Variation at Output                            | Δ.                                   | Management at V                                                                                        |   | -    | -     | 4    | %     |

| OVP Variation at Output                            | $\Delta_{\text{OVP}}$                | Measured at $V_{OUT}$ when $R_{OVP}$ = 188 kΩ                                                          | • | -    | _     | 7    | %     |

| Lindon salta va Dataatian Thurshald                |                                      | Measured at V <sub>OUT</sub> when R <sub>OVP</sub> = 188 kΩ <sup>[2]</sup>                             |   | 2.4  | 2.55  | 2.7  | V     |

| Undervoltage Detection Threshold                   | V <sub>UVP(th)</sub>                 | Measured at $V_{OUT}$ when $R_{OVP} = 0 \Omega$                                                        |   | 0.13 | 0.20  | 0.25 | V     |

| BOOST SWITCH GATE DRIVER                           |                                      |                                                                                                        |   |      |       |      |       |

| Gate Driver Supply Voltage                         | V <sub>DRV</sub>                     | Measured at V <sub>IN</sub> > 7.5 V                                                                    |   | -    | 6.5   | -    | V     |

| Gate Driver Pull-Up and Pull-Down                  | R <sub>GDRV</sub>                    | Measured at i <sub>GDRV</sub> = 100 mA                                                                 |   | -    | 2.5   | -    | Ω     |

| Gate Pull-Down When Disabled                       | R <sub>GDRV_OFF</sub>                | EN = L, V <sub>IN</sub> = 0 V                                                                          |   | -    | 100   | -    | kΩ    |

| Peak Sink Current [2]                              | İ <sub>SINK</sub>                    | Measured at V <sub>GDRV</sub> = V <sub>DRV</sub>                                                       |   | -    | 2     | -    | Α     |

| Peak Source Current [2]                            | i <sub>SOURCE</sub>                  | Measured at V <sub>GDRV</sub> = 0 V                                                                    |   | -    | 2     | -    | Α     |

| Gate Rise / Fall Time [2]                          | t <sub>RISE,</sub> t <sub>FALL</sub> | Measured with C <sub>LOAD</sub> = 1.5 nF;<br>V <sub>GDRV</sub> between 10% and 90% of V <sub>DRV</sub> |   | _    | 7     | -    | ns    |

| Minimum Gate Driver On-Time                        | t <sub>SW(ON)</sub>                  |                                                                                                        | • | -    | -     | 100  | ns    |

| Minimum Gate Driver Off-Time                       | t <sub>SW(OFF)</sub>                 |                                                                                                        | • | -    | _     | 100  | ns    |

| BOOST SWITCH CURRENT SENS                          |                                      |                                                                                                        |   |      |       |      |       |

| Primary Current Sense Limit                        | i <sub>CS(LIM1)</sub>                | Exceeding i <sub>CS(LIM1)</sub> causes gate driver to truncate existing cycle, but does not shut down  | • | 175  | 210   | 245  | mV    |

| Secondary Current Sense Limit [2]                  | i <sub>CS(LIM2)</sub>                | Exceeding i <sub>CS(LIM2)</sub> causes gate driver to shut down and latch off                          |   | -    | 300   | -    | mV    |

| Secondary Current Sense Limit<br>Propagation Delay | t <sub>CSDELAY</sub>                 | Overdrive CS threshold by 10%, excluding leading edge blanking                                         |   | -    | 32    | -    | ns    |

| OSCILLATOR FREQUENCY                               |                                      |                                                                                                        |   |      |       |      |       |

| Ossillator Fraguency                               | f                                    | $R_{FSET} = 10 \text{ k}\Omega$                                                                        | • | 1.95 | 2.15  | 2.35 | MHz   |

| Oscillator Frequency                               | f <sub>SW</sub>                      | R <sub>FSET</sub> = 110 kΩ                                                                             |   | -    | 200   | ı    | kHz   |

| FSET Pin Voltage                                   | V <sub>FSET</sub>                    | $R_{FSET}$ = 10 k $\Omega$                                                                             |   | -    | 1.00  | -    | V     |

| SYNCHRONIZATION                                    |                                      |                                                                                                        |   |      |       |      |       |

| Cyna Innyt Logia Loyal                             | V <sub>SYNCL</sub>                   | FSET/SYNC pin logic Low                                                                                | • | -    | _     | 0.4  | V     |

| Sync Input Logic Level                             | V <sub>SYNCH</sub>                   | FSET/SYNC pin logic High                                                                               | • | 1.5  | _     | _    | V     |

| Synchronized PWM Frequency                         | f <sub>SWSYNC</sub>                  |                                                                                                        | • | 260  | _     | 2300 | kHz   |

| Synchronization Input Min Off-Time                 | t <sub>PWSYNCOFF</sub>               |                                                                                                        | • | 150  | _     | _    | ns    |

| Synchronization Input Min On-Time                  | t <sub>PWSYNCON</sub>                |                                                                                                        | • | 150  | -     | -    | ns    |

Continued on the next page...

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

ELECTRICAL CHARACTERISTICS [1] (continued): Unless otherwise noted, specifications are valid at  $V_{IN}$  = 12 V,  $T_J$  = 25°C, • indicates specifications guaranteed over the full operating temperature range with  $T_J$  = -40°C to 125°C, typical specifications are at  $T_J$  = 25°C

| Characteristics                                                | Symbol                 | Test Conditions                                                                                                                                |                                |   | Min.  | Тур.  | Max.  | Unit   |

|----------------------------------------------------------------|------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---|-------|-------|-------|--------|

| LED CURRENT SINKS                                              | J.                     |                                                                                                                                                |                                |   |       |       |       |        |

| LEDx Accuracy [4]                                              | Err <sub>LED</sub>     | $i_{ISET}$ = 120 μA ( $R_{ISET}$ = 8.33 kΩ)                                                                                                    |                                | • | -     | 0.7   | 3     | %      |

| LEDx Matching                                                  | $\Delta_{LEDx}$        | i <sub>ISET</sub> = 120 μA                                                                                                                     |                                | • | -     | 0.8   | 2     | %      |

|                                                                |                        | Measured individually with all                                                                                                                 | A80602                         | • | 650   | 750   | 850   | mV     |

| LEDx Regulation Voltage                                        | V <sub>LED</sub>       | other LED pins tied to ≥1 V,<br>i <sub>ISET</sub> = 120 μA, V <sub>ADIM</sub> > 2.1 V                                                          | A80602-1                       | • | 760   | 860   | 960   | mV     |

| I <sub>ISET</sub> to I <sub>LEDx</sub> Current Gain            | A <sub>ISET</sub>      | i <sub>ISET</sub> = 120 μA                                                                                                                     |                                | • | 955   | 978   | 1000  | A/A    |

| ISET Pin Voltage                                               | V <sub>ISET</sub>      | V <sub>ADIM</sub> > 2.1 V                                                                                                                      |                                |   | 0.955 | 0.985 | 1.015 | V      |

| Allowable ISET Current                                         | İ <sub>ISET</sub>      | V <sub>ADIM</sub> > 2.1 V                                                                                                                      |                                | • | 20    | -     | 144   | μA     |

| LED String Partial-Short Detect                                | V <sub>LEDSD</sub>     | Sensed from each LED pin to GND sink is in regulation; all other LED pir                                                                       |                                | • | 4.9   | 5.5   | 6.1   | V      |

| LED Pin Shorted-to-GND Test Duration [2]                       | t <sub>LEDSTG</sub>    | Wait time before proceeding with no LED pin is shorted to GND)                                                                                 | Soft-Start (if                 |   | -     | 1.5   | -     | ms     |

| Soft-Start Ramp-Up Time [2]                                    | t <sub>SSRU</sub>      | Maximum time duration before al channels come into regulation, or tripped, whichever comes first                                               |                                |   | 6.6   | 8.2   | 9.8   | ms     |

| Enable Pin Shut Down Delay                                     | t <sub>EN(OFF)</sub>   | EN goes from High to Low; exceed results in IC shutdown                                                                                        | eding t <sub>EN(OFF)</sub>     | • | 10    | 16    | 22    | ms     |

| Minimum PWM On-Time                                            | t <sub>PWMH</sub>      | First and subsequent PWM pulse                                                                                                                 | es                             | • | _     | 0.3   | 0.4   | μs     |

| Minimum PWM Off-Time<br>(for PWM ≠ 100%) [2]                   | t <sub>PWMLOW</sub>    | Externally pulsing PWM pin                                                                                                                     |                                | • | -     | _     | 1     | μs     |

| INPUT DISCONNECT GATE PIN                                      |                        |                                                                                                                                                |                                |   |       |       |       |        |

| Gate Pin Sink Current                                          | I <sub>GSINK</sub>     | V <sub>GS</sub> = V <sub>IN</sub> , no input OCP fault                                                                                         |                                |   | -     | -113  | _     | μA     |

| Gate Pin Source Current                                        | I <sub>GSOURCE</sub>   | $V_{GS} = V_{IN} - 6 V$ , input OCP fault t                                                                                                    | tripped                        |   | -     | 6     | -     | mA     |

| Gate Shutdown Delay When Over-<br>Current Fault Is Tripped [2] | t <sub>GATEFAULT</sub> | V <sub>IN</sub> – V <sub>SENSE</sub> = 200 mV; monitored                                                                                       | d at FAULT pin                 |   | -     | _     | 3     | μs     |

| Gate Voltage                                                   | V <sub>GS</sub>        | PMOS Gate to source voltage me gate is on                                                                                                      | easured when                   |   | -     | -6.7  | -     | V      |

| VSENSE PIN                                                     |                        |                                                                                                                                                |                                |   |       |       |       |        |

| VSENSE Pin Sink Current                                        | i <sub>ADJ</sub>       |                                                                                                                                                |                                | • | 16    | 20    | 24    | μA     |

| VSENSE Trip Point                                              | V <sub>SENSETRIP</sub> | Measured between $V_{IN}$ and $V_{SEN}$                                                                                                        | $_{SE}$ , $R_{ADJ} = 0 \Omega$ | • | 88    | 98    | 108   | mV     |

| FAULT PIN                                                      |                        |                                                                                                                                                |                                |   |       |       |       |        |

| FAULT Output Pull-Down Voltage                                 | V <sub>FAULT</sub>     | i <sub>FAULT</sub> = 1 mA                                                                                                                      |                                |   | -     | _     | 0.5   | V      |

| FAULT Pin Leakage Current                                      | I <sub>FAULT-LKG</sub> | V <sub>FAULT</sub> = 5 V                                                                                                                       |                                |   | -     | _     | 1     | μA     |

| External FAULT Input Low                                       | V <sub>FIL</sub>       | No internal faults; FAULT pin externally pulled down                                                                                           |                                | • | -     | _     | 0.8   | V      |

| External FAULT Input High                                      | V <sub>FIH</sub>       | No internal faults                                                                                                                             |                                | • | 1.5   | _     | _     | V      |

| External FAULT Deglitch Timer                                  | t <sub>FIL</sub>       | No internal faults; delay (in f <sub>SW</sub> cycles) from FAULT pin externally pulled L to LED off; ignored if FAULT returns to H before that |                                |   | _     | 8     | _     | cycles |

| THERMAL PROTECTION (TSD)                                       |                        |                                                                                                                                                |                                |   |       |       |       |        |

| Thermal Shutdown Threshold [2]                                 | T <sub>SD</sub>        | Temperature rising                                                                                                                             |                                |   | 155   | 170   | -     | °C     |

| Thermal Shutdown Hysteresis [2]                                | T <sub>SDHYS</sub>     |                                                                                                                                                |                                |   | -     | 20    | _     | °C     |

<sup>[1]</sup> For input and output current specifications, negative current is defined as coming out of the node or pin (sourcing);

<sup>[4]</sup> LED current is trimmed to cancel variations in both Gain and ISET voltage.

positive current is defined as going into the node or pin (sinking). [2] Ensured by design and characterization; not production tested.

<sup>[3]</sup> Minimum  $V_{IN} = 4.5 \text{ V}$  is only required at startup. After startup is completed, IC can continue to operate down to  $V_{IN} = 4 \text{ V}$ .

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **FUNCTIONAL DESCRIPTION**

The A80602 is a multi-string LED regulator with six precision current sinks and a gate driver for external boost MOSFET switch. It incorporates a patented Pre-Emptive Boost (PEB) control algorithm to achieve PWM dimming ratio over 15,000:1 at 200 Hz under nominal application conditions. PEB control also minimizes output ripple to avoid audible noise from output ceramic capacitors.

The switching frequency can be either synchronized to an external clock or generated internally. Spread-spectrum technique (with user-programmable dithering range and modulation frequency) is provided to reduce EMI.

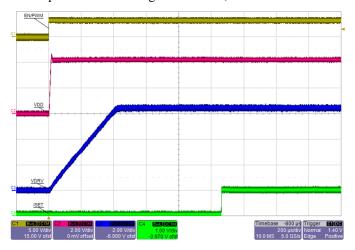

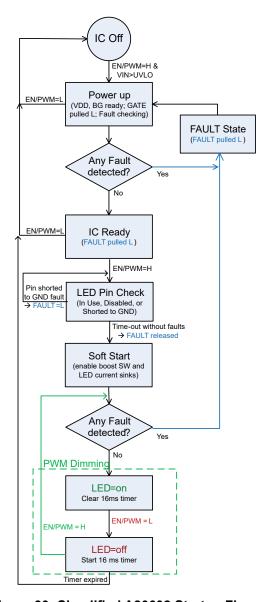

#### **Enabling the IC**

The A80602 wakes up when EN/PWM pin is pulled above logic high level, if VIN pin voltage is over the VIN\_UVLO threshold. The boost stage and LED channels are enabled separately by PWM = H signal after the IC powers up.

The IC performs a series of safety checks at power up, to determine if there are possible fault conditions that might prevent the system from functioning correctly. Power-up checks include:

- VOUT shorted to GND

- LED pin shorted to GND

- FSET pin open/shorted

- ISET pin open/shorted to GND, etc.

Only if no faults were detected, then the IC can proceed to start switching.

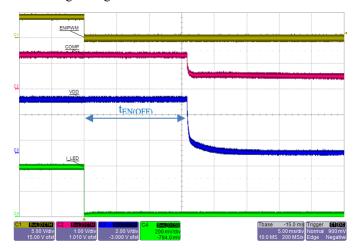

During operation, the EN/PWM pin can be toggled to control the brightness of LEDs channels by using PWM dimming. If EN/PWM is pulled Low for longer than 16ms, the IC shuts off.

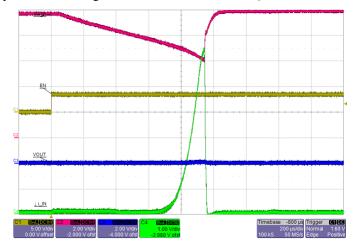

Figure 3: Startup showing (from top to bottom) EN/PWM, VDD, VDRV, and ISET.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **Powering Up: LED Detection Phase**

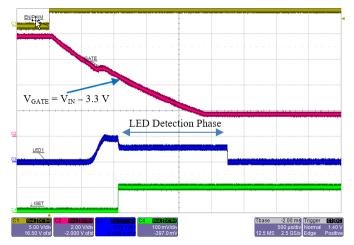

The VIN pin has an undervoltage lockout (UVLO) function that prevents the A80602 from powering up until the UVLO threshold is reached. Once the VIN pin goes above UVLO and a high signal is present on the EN pin, the IC proceeds to power up. At this point, the A80602 enables the disconnect switch and tries to check if any LED pins are shorted to GND and/or are not used. The LED detection phase starts when the GATE voltage of the input disconnect PMOS switch is pulled down to 3.3 V below  $V_{\rm IN}$ .

Figure 4: Startup showing EN/PWM, GATE, LED1, and ISET. Note that LED Detection Phase starts as soon as GATE pin is pulled down to 3.3 V below  $\rm V_{IN}$ .

Once the voltage threshold on VLED pins exceeds  $\sim$ 120 mV, a delay of approximately 1.5 ms is used to determine the status of the pins.

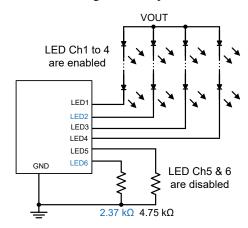

Unused LED pins should be terminated with a resistor to GND. Value of this termination resistor is 4.75 k $\Omega$  for channel 1, 3, 4, 5; or 2.37 k $\Omega$  for channel 2, 6. At the end of LED detection phase, any channel with pull-down resistor is then disabled and does not contribute to the boost regulation loop.

Figure 5: How to signal an unused LED channel during startup LED detection phase

Table 1: LED Detection phase voltage threshold levels

| LED Pin<br>Voltage Measured | Interpretation                  | Outcome                                                |

|-----------------------------|---------------------------------|--------------------------------------------------------|

| < 120 mV                    | LED pin shorted to<br>GND fault | Cannot proceed with soft-start unless fault is removed |

| ~230 mV                     | LED channel not in use          | LED channel is removed from operation                  |

| > 340 mV                    | LED channel in use              | Proceed with soft-start                                |

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

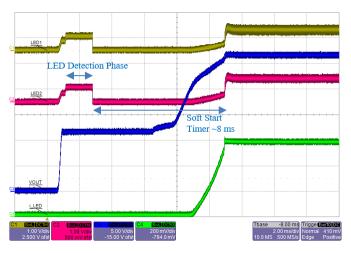

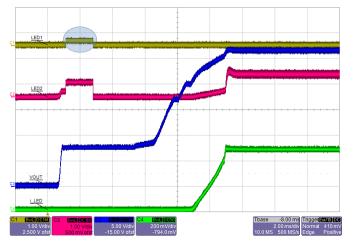

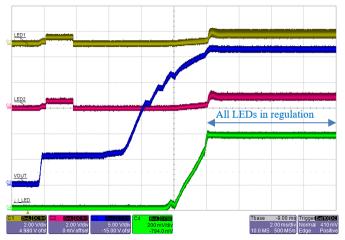

Figure 6: Normal startup showing all channels passed LED Detection phase (only LED1 and LED2 pin voltages are shown). Output Voltage = 26.5 V (8× LED). Total LED current = 100 mA × 6.

Figure 7: Normal startup showing LED1 channel is disabled with a 4.75 k $\Omega$  resistor to GND. Total LED current = 100 mA × 5.

If an LED pin is shorted to ground, the A80602 does not proceed with soft start until the short is removed from the LED pin. This prevents the A80602 from ramping up the output voltage and putting an uncontrolled amount of current through the LEDs.

The FAULT pin is pulled low in case of LED pin shorted-to-GND fault, but the IC continues to retry. Once the fault is removed, the soft-start process continues. The same applies in case of FSET or ISET pin is shorted to GND.

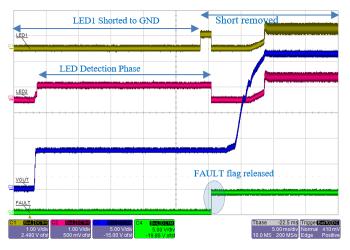

Figure 8: LED1 is shorted-to-GND initially, then released. After the fault is removed, the IC auto-recovers and proceeds with soft-start.

FAULT is released at the end of LED detection phase.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### Power Up: Boost Output Undervoltage

During startup, after the input disconnect switch has been enabled, the output voltage is checked through the OVP (overvoltage protection) pin. If the sensed voltage does not rise above  $V_{\rm UVP(th)}$ , the output is assumed to be at fault and the IC does not proceed with soft start. Output UVP level is linked to the OVP level programmed according to the equation:

$$V_{UVP} = V_{OVP} / 12$$

Undervoltage protection may be caused by one of the following faults:

- · Output capacitor shorted to GND

- Boost inductor or diode open

- · OVP sense resistor open

After an UVP (undervoltage protection) fault, the A80602 is immediately shutdown and latched off. To enable the IC again, the latched fault must be cleared. This can be achieved by powering-cycling the IC, which means either:

- $\bullet$  V<sub>IN</sub> falls below falling UVLO threshold, or

- EN = L for > 16 ms.

Alternatively, latched fault can be cleared by keeping EN = H but pulling PWM = L for >16 ms. This method has the advantage that it does not reset the IC.

#### Soft Start Function

During startup, the A80602 ramps up its boost output voltage following a fixed slope, as determined by OVP set point and Soft-Start Timer. This technique limits the input inrush current and ensures consistent startup time regardless of the PWM dimming duty cycle.

The soft-start process is completed when any one of the following conditions is met:

- All enabled LED channels have reached their regulation current,

- Output voltage has reached 93% of its OVP threshold, or

- Soft-start ramp time (t<sub>SS</sub>) has expired.

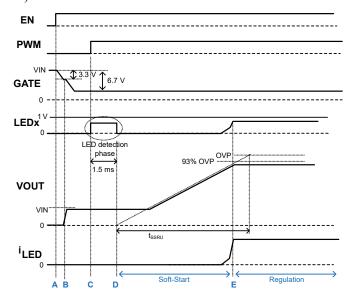

To summarize, the complete startup process of A80602 consists of:

- · Power-up error checking

- · Enabling input disconnect switch

- LED pin open/short detection

- Soft-start ramp

This is illustrated by the following startup timing diagram (not to scale):

Figure 9: Complete startup process of A80602

Explanation of Events:

- A: EN = H wakes up the IC.  $V_{DD}$  ramps up. IC starts to pull down GATE slowly.

- **B**: When GATE is pulled down to 3.3 V below  $V_{IN}$ ,  $I_{SET}$  becomes enabled. IC is now waiting for PWM = H to startup.

- **C**: Once PWM = H, the IC checks each LEDx pins to determine if it is in use, disabled, or shorted to GND.

- D: Soft-Start begins at the completion of LED pin short-detect phase of  $\sim$ 1.5 ms.  $V_{OUT}$  ramps up following a fixed slope set by OVP and soft-start timer of  $\sim$ 8 ms.

- **E**: Soft-start terminates when all LED currents reached regulation, V<sub>OUT</sub> reached 93% OVP, or soft-start timer expired.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

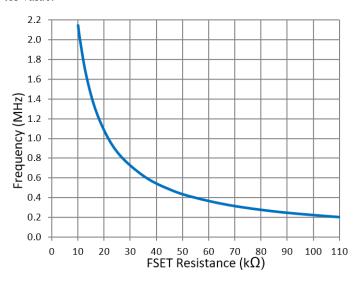

#### **Frequency Selection**

The switching frequency of the boost regulator is programmed by a resistor connected to FSET pin. The switching frequency can be selected anywhere from 260 kHz to 2.3 MHz. The chart below shows the typical switching frequency verses FSET resistor value.

Figure 10: Switching Frequency as a function of FSET Resistance

Alternatively, the following empirical formula can be used:

Equation 1:  $R_{FSET} = (21.5 / f_{SW}) - 0.2$

where  $f_{SW}$  is in MHz and  $R_{FSET}$  is in  $k\Omega.$

If a fault occurs during operation that increases the switching frequency, the internal oscillator frequency is clamped to a maximum of 3.5 MHz. If the FSET pin is shorted to GND, then the part shuts down. For more details, refer to the Fault Mode Table section.

#### **Synchronization**

The A80602 can also be synchronized using an external clock from 260 kHz to 2.3 MHz. At power up, if the FSET pin is held low, then the IC does not start. Only when the FSET pin is tri-stated to allow for the pin to rise to about 1 V, or when a sync clock is detected, the A80602 then tries to power up.

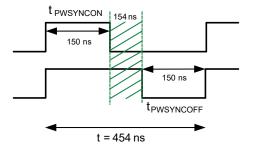

The basic requirement of the external sync signal is 150 ns minimum on-time and 150 ns minimum off time. The diagram below shows the timing restrictions for a synchronization clock at 2.2 MHz.

Figure 11: Pulse width requirements for an External Sync clock at 2.2 MHz

Based on the above, any clock with a duty cycle between 33% and 66% at 2.2 MHz can be used. The table below summarizes the allowable duty cycle range at various synchronization frequencies.

Table 2: Acceptable Duty Cycle range for External Sync clock at various frequencies

| Sync. Pulse Frequency | Duty Cycle Range |

|-----------------------|------------------|

| 2.2 MHz               | 33% to 66%       |

| 2 MHz                 | 30% to 70%       |

| 1 MHz                 | 15% to 85%       |

| 600 kHz               | 9% to 91%        |

| 300 kHz               | 4.5% to 95.5%    |

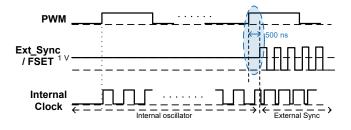

If it is necessary to switch over between internal oscillator and external sync during operation, ensure the transition takes place at least 500 ns after the previous PWM = H rising edge. Alternatively, execute the switchover during PWM = L only. This restriction does not apply if PWM dimming is not being used.

Figure 12: Avoid switching over between Internal Oscillator and External Sync in highlighted region

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### Loss of External Sync Signal

Suppose the A80602 started up with a valid external SYNC signal, but the SYNC signal is lost during normal operation. In that case, one of the following happens:

- If the external SYNC signal is high impedance (open), the IC continues normal operation after approximately 5 µs, at the switching frequency set by R<sub>FSET</sub>. No FAULT flag is generated.

- If the external SYNC signal is stuck low (shorted to ground), the IC detects an FSET-shorted-to-GND fault. FAULT pin is pulled low after approximately 10 µs, and switching is disabled. Once the FSET pin is released or SYNC signal is detected again, the IC proceeds to soft-start.

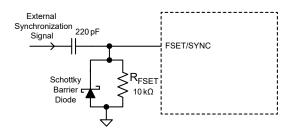

To prevent generating a fault when the external SYNC signal is stuck at low, the circuit shown below can be used. When the external SYNC signal goes low, the IC continues to operate normally at the switching frequency set by the  $R_{\rm FSET}$ . No FAULT flag is generated.

Figure 13: Countermeasure for External Sync Stuck-at-Low Fault

It is important to use a small capacitance for the AC-coupling capacitor (220 pF in the above example). If the capacitance is too large, the IC may incorrectly declare a FSET-shorted-to-GND fault and restart.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### Switching Frequency Dithering

To minimize the peak EMI spikes at switching frequency harmonics, the A80602 offers the option of frequency dithering, or spread-spectrum clocking. This feature simplifies the input filters needed to meet the automotive CISPR 25 conducted and radiated emission limits.

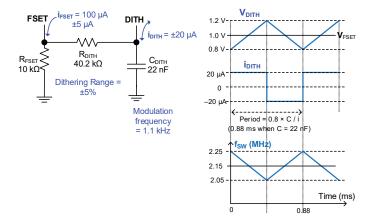

For maximum flexibility, the A80602 allows both dithering range and modulation frequency to be independently programmable using two external components.

The Dithering Modulation Frequency capacitor value is determined by using the approximate equation:

Equation 2:

$$C_{DITH}$$

(nF) = 25 /  $f_{DM}$  (kHz)

where  $C_{\mbox{\scriptsize DITH}}$  is the value of capacitor connected from DITH pin to GND.

The resistor that sets the dithering range is calculated using:

Equation 3:

$$R_{DITH} = 20 \times R_{FSET} / Range (\pm\%)$$

where  $R_{FSET}$  is the resistor from FSET pin to GND,  $R_{DITH}$  is the resistor between DITH and FSET pins.

As an example, by using  $R_{FSET}=10~k\Omega$ ,  $R_{DITH}=40.2~k\Omega$ , and  $C_{DITH}=22~nF$ , the resulted switching frequency is  $f_{SW}=2.15~MHz\pm5\%$  modulated at 1.1 kHz. This is illustrated by the following diagram.

Figure 14: How to Program Switching Frequency Dithering Range and Modulation Frequency

There are no hard limits on dithering range and modulation frequency. As a general guideline, pick a dithering range between ±5% and 10%, with the modulation frequency between 1 kHz and 3 kHz. In practice, using a larger dithering range and/or higher modulation frequency do not generate any noticeable benefits.

If dithering function is not desired, it can be disabled by disconnecting the  $R_{\rm DITH}$  between DITH and FSET pins. Connect DITH pin to VDD if  $C_{\rm DITH}$  is not populated. Dithering is always disabled when  $f_{\rm SW}$  is controlled by external sync.  $R_{\rm DITH}$  and  $C_{\rm DITH}$  have no effects in this case even if they were populated.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **LED Current Setting**

The maximum LED current can be up to 140 mA per channel and is set through the ISET pin. Connect a resistor  $R_{\rm ISET}$  between this pin and GND. The relation between  $I_{\rm LED}$  and  $R_{\rm ISET}$  is given below:

Equation 4:

$$\begin{split} I_{LED} &= I_{SET} \times A_{ISET} \\ I_{SET} &= V_{ISET} / R_{ISET} \\ Therefore &\, R_{ISET} = (V_{ISET} \times A_{ISET}) \, / \, I_{LED} \\ &= 963 \, / \, I_{LED} \end{split}$$

where  $I_{LED}$  current is in mA and  $R_{ISET}$  is in k $\Omega$ .

This sets the maximum current through the LEDs, referred to as the '100% current'. The average LED current can be reduced from the 100% current level by using either PWM dimming or analog dimming.

Table 3: ISET resistor values vs. LED current. Resistances are rounded to the nearest E-96 (1%) resistor value.

| Standard Closest RISET<br>Resistor Value | LED current per channel |

|------------------------------------------|-------------------------|

| 6.81 kΩ                                  | 140 mA                  |

| 9.53 kΩ                                  | 100 mA                  |

| 12 kΩ                                    | 80 mA                   |

| 16 kΩ                                    | 60 mA                   |

| 24 kΩ                                    | 40 mA                   |

#### **PWM Dimming**

When the EN/PWM pin is pulled high, the A80602 turns on all enabled LED current sinks. When it is pulled low, all LED current sinks are turned off. By changing the duty cycle of PWM signal, the average LED current (and hence brightness) can be accurately controlled.

During PWM = L, the IC floats the compensation (COMP) pin and waits for the next PWM rising edge. But if PWM stays Low longer than  $t_{\rm EN(OFF)}$  duration (16 ms typical), the IC shuts off completely.

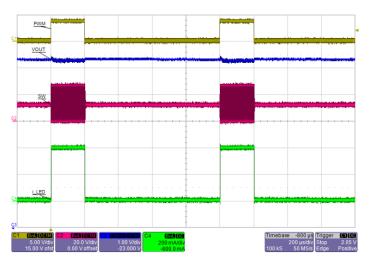

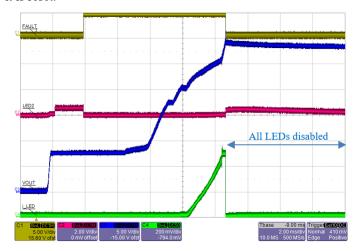

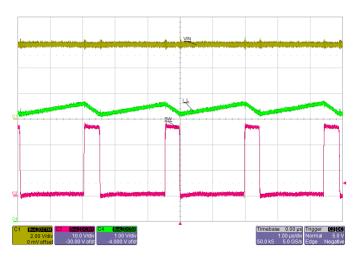

Figure 15: PWM dimming operation at 20% 1 kHz. CH1 = PWM (5 V/div), CH2 = SW (20 V/div), CH3 =  $V_{OUT}$ , CH4 =  $I_{LED}$  (200 mA/div).

By using the patented Pre-Emptive Boost (PEB) control algorithm, the A80602 can achieve minimum PWM dimming on-time down to 300 ns. This translates to PWM dimming ratio up to 15,000:1 at the PWM dimming frequency of 200 Hz under nominal application conditions. Technical details on PEB is explained in the next section.

Figure 16: Zoom in view for PWM on-time = 10  $\mu$ s. Notice that the LED current is shifted with respect to PWM signal. Ripple at V<sub>OUT</sub> is ~0.2 V when using 2 × 4.7  $\mu$ F MLCC as output capacitors.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

Figure 17: Zoom-in view showing A80602 is able to regulate LED current at PWM on-time down to 300 ns.

The typical PWM dimming frequencies fall between 200 Hz and 1 kHz. There is no hard limit on the highest PWM dimming frequency that can be used. However, at higher PWM frequency, the maximum PWM dimming ratio is reduced. This is shown in the following table:

Table 4: Maximum PWM Dimming Ratio that can be achieved when operating at different PWM Dimming Frequency

| PWM Frequency | PWM Period | Maximum PWM<br>Dimming Ratio |

|---------------|------------|------------------------------|

| 200 Hz        | 5 ms       | 15,000:1                     |

| 1 kHz         | 1 ms       | 3,000:1                      |

| 3.3 kHz       | 300 µs     | 1,000:1                      |

| 20 kHz        | 50 μs      | 150:1                        |

While it is possible to operate with very high PWM duty cycle for subtle dimming, it is important to avoid PWM pulse low periods that are shorter than the Minimum PWM Off-Time ( $t_{PWM-LOW}$ ), which is 1  $\mu$ s. Driving PWM at 100% is acceptable.

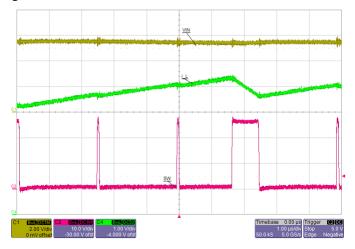

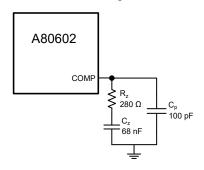

#### **Pre-Emptive Boost**

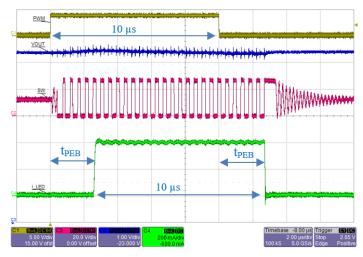

The basic principle of pre-emptive boost (PEB) can be best explained by the following two waveforms. The first one shows how a conventional LED driver operates during PWM dimming operation. The second one shows that of the A80602.

Common test conditions for both cases:

PWM = 1% at 1 kHz (on-time = 10 μs),  $f_{SW}$  = 2.15 MHz, L = 10 μH,  $V_{IN}$  = 12 V, LED load = 8 series ( $V_{OUT}$  = ~25 V) at 100 mA × 4.  $C_{OUT}$  = 2 × 4.7 μF 50 V 1210 MLCC. COMP:  $R_Z$  = 280  $\Omega$ ,  $C_Z$  = 68 nF.

#### Common scope settings:

CH1 (Yellow) = PWM (5 V/div); CH2 (Red) = Inductor current (500 mA/div); CH3 (Blue) = V<sub>OUT</sub> (1 V/div); CH4 (Green) = LED current (200 mA/div); time scale = 2 µs/div.

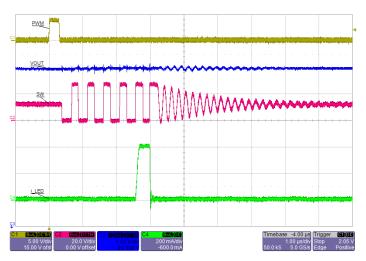

Figure 18: Traditional PWM Dimming operation where boost switch and LED current are enabled at the same time. Note that  $V_{OUT}$  shows overall ripple of  $\sim 0.5~V$

When PWM signal goes high, a conventional LED driver turns on its boost switching at the time with LED current sinks. The problem is that the inductor current takes several switching cycles to ramp up to its steady-state value before it can deliver full power to the output load. During the first few cycles, energy to the LED load is mainly supplied by the output capacitor, which results in noticeable dip in output voltage.

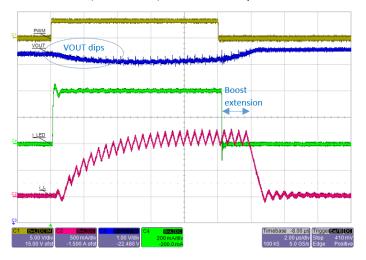

Figure 19: A80602 PWM dimming operation with PEB delay set to 3  $\mu$ s. Note that  $V_{OUT}$  ripple is reduced to ~0.2 V.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

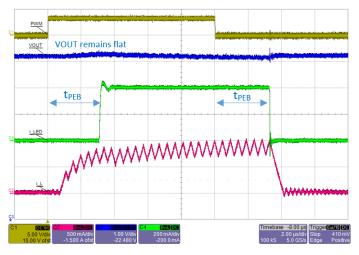

In the A80602, the boost switch is also enabled when PWM goes high. However, the LED current is not turned on until after a short delay of  $t_{PEB}$ . This allows the inductor current to build up before it starts to deliver the full power to LED load. During the pre-boost period,  $V_{OUT}$  bumps up very slightly, while the following dip is essentially eliminated. When PWM goes low, both boost switching and LED remains active for the same delay of  $t_{PEB}$ . Therefore, the PWM on-time is preserved in LED current.

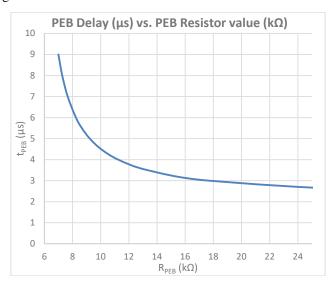

PEB delay can be programmed using an external resistor,  $R_{\text{PEB}}$ , from PEB pin to GND. Their relationship is shown in the following chart:

Figure 20: How PEB delay time varies with value of PEB pin resistor to GND.

Ideally,  $t_{PEB}$  is equal to the inductor current ramp up time. But the latter is affected by many external parameters, such as switching frequency, inductance,  $V_{IN}$  and  $V_{OUT}$  ratio, etc. Therefore, some experimentation is required to optimize the PEB delay time. In general, for switching frequency at 2 MHz,  $t_{PEB}$  = 2.5 to 4  $\mu s$  is a good starting point.

The advantage of PEB is that even a non-optimized delay time can significantly reduce the output ripple voltage compared to a conventional LED driver.

#### **Analog Dimming**

The peak (100%) level of LED current is set by the  $R_{\rm ISET}$  resistor. The actual peak LED current may also be adjusted continuously from approximately 10% up to 100%, by using the ADIM pin. There are two methods to do so:

- 1. In ADIM mode: apply a DC voltage between 0.2 V and 2 V at the pin.

- 2. In APWM mode: apply a clock signal with required duty cycle at the pin.

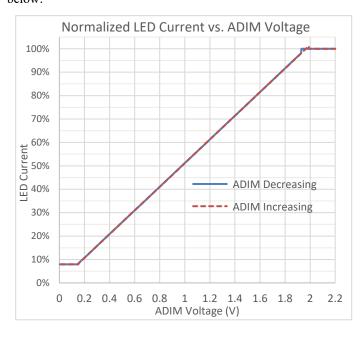

#### **ADIM MODE**

An analog voltage is applied at the ADIM pin. This DC voltage linearly controls the peak LED current, as illustrated by the chart below:

Figure 21: In analog dimming mode, the LED current is linearly proportional to ADIM voltage between 0.2 V and 2 V approximately

There is an internal pull-down resistor (50 k $\Omega$  typical) from ADIM pin to GND. When this pin is left floating, LED current is being dimmed down to ~10%. Therefore, if analog dimming is not required, the ADIM pin should be pulled to over 2 V (but below  $V_{DD}$ ) to ensure 100% LED current. One simple technique is to pull up ADIM to VDD through a 30 k $\Omega$  resistor.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

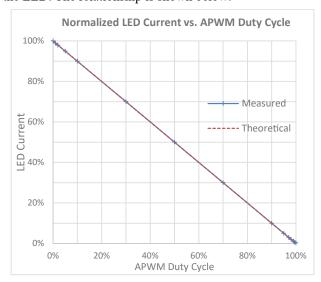

#### **APWM MODE**

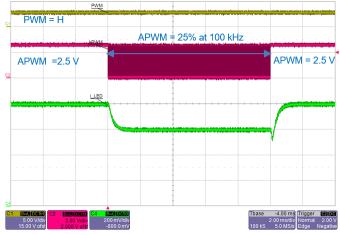

When a clock signal is detected at ADIM pin, the A80602 goes into APWM mode. The typical APWM signal frequency is between 40 kHz and 1 MHz. The duty cycle of this signal is inversely proportional to the percentage of current delivered to the LED. The relationship is shown below:

Figure 22: Showing LED current is inversely proportional to the APWM duty cycle. Test conditions:  $V_{IN}$  = 12 V,  $V_{OUT}$  = 25 V (8 × WLED), total LED current = 100 mA × 4, APWM frequency = 100 kHz

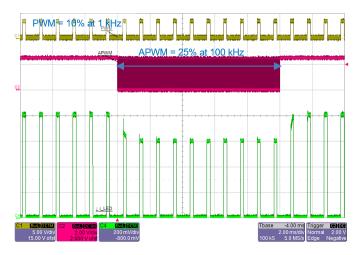

As an example, a system that delivers a full LED current of 100 mA per channel would deliver 75 mA when an APWM signal with a duty-cycle of 25% is applied (because analog dimming level is 100% - 25% = 75%). This is demonstrated by the following waveforms (only LED channels 1 to 4 are enabled).

Figure 23: PWM = H. Total LED current drops from 400 mA (4 × 100 mA/ch) to 300 mA when APWM of 25% duty cycle is applied. Note that LED current takes ~1 ms to settle after change in APWM.

Figure 24: PWM = 10% at 1 kHz. Peak LED current drops from 400 mA (4  $\times$  100 mA/ch) to 300 mA when APWM of 25% duty cycle is applied

While in APWM mode, if a clock pulse is not detected within  $\sim \! 50~\mu s$ , the IC falls back to ADIM mode. To ensure reliable detection of APWM clock, its on-time and off-time must be at least 150 ns. Therefore, the allowable APWM duty cycle range is dependent on the APWM frequency, as shown in the table below:

Table 5: Acceptable Duty Cycle range for APWM clock at various frequencies

| APWM Frequency | APWM Duty Cycle |

|----------------|-----------------|

| 40 kHz         | 0.6% to 99.4%   |

| 100 kHz        | 1.5% to 98.5%   |

| 300 kHz        | 4.5% to 95.5%   |

| 1 MHz          | 15% to 85%      |

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

One popular application of analog dimming is for LED brightness calibration, commonly known as 'LED Binning'. LEDs from the same manufacturer and series are often grouped into different 'bins' according to their light efficacy (lumens per watt). It is therefore necessary to calibrate the '100% current' for each LED bin, in order to achieve uniform luminosity.

To use ADIM pin as a trim function, the user should first set the 100% current based on efficacy of LED from the lowest bin. When using LED with higher efficacy, the required current is then trimmed down to the appropriate level using APWM duty cycle.

As an example, assume that:

- LED from lowest bin has an efficacy of 80 lm/W

- LED highest bin has an efficacy of 120 lm/W

Suppose the maximum LED current was set at 100 mA based on LEDs from lowest bin. When using LEDs from highest bin, the current should then be reduced to 67% (80/120). This can be achieved by sending APWM clock with 33% duty cycle.

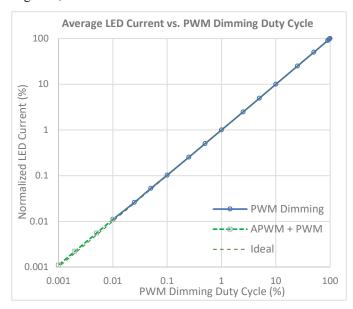

#### **Extending LED Dimming Ratio**

The dynamic range of LED brightness can be further extended, by using a combination of PWM duty cycle, APWM duty cycle, and analog dimming method.

For example, the following approach can be used to achieve a 100,000:1 dimming ratio at 200 Hz:

- Vary PWM duty cycle from 100% down to 0.01% to give 10,000:1 dimming. This requires PWM dimming on-time be reduced down to 0.5 μs.

- With PWM dimming on-time fixed at 0.5 μs, reduce peak LED current from 100% down to 10%. This can be achieved by either:

- □ Apply a clock signal at ADIM pin, and vary its duty cycle from 1.5% to 90% (at 100 kHz), or

- □ Apply a DC voltage at ADIM pin, and vary its level from 2 V down to 0.2 V.

The net result of using both PWM and APWM is 100,000:1 dimming ratio, as shown in the chart below:

Figure 25: How to achieve 100,000:1 dimming ratio by using both PWM and APWM. Test conditions:  $V_{\rm IN}$  = 12 V,  $V_{\rm OUT}$  = 25 V (8 × WLED), total LED current = 400 mA, PWM frequency = 200 Hz, APWM frequency = 100 kHz.

Note that the A80602 can provide analog dimming range greater than 10:1. By applying APWM with 96% duty cycle, for example, an analog dimming range of 25:1 can be achieved. However, this requires the external APWM signal source to have very fine pulse-width resolution. At 200 kHz APWM frequency, a resolution of 50 ns is required to adjust its duty cycle by 1%.

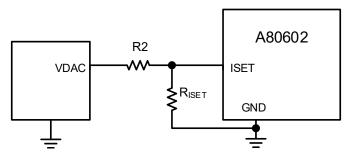

#### **Analog Dimming with External Voltage**

Besides using ADIM pin, the LED current can also be reduced by using an external voltage source applied through a resistor to the ISET pin. The dynamic range of this type of dimming is dependent on the ISET pin current. The recommended  $i_{SET}$  range is from 20  $\mu A$  to 144  $\mu A$  for the A80602. Note that the IC continues to work at  $i_{SET}$  below 20  $\mu A$ , but the relative error in LED current becomes larger at lower dimming level.

Below is a typical application circuit using a DAC (digital-analog converter) to control the LED current. The ISET current (which directly controls the LED current) is normally set as  $V_{\rm ISET}/R_{\rm ISET}$ . The DAC voltage can be higher or lower than  $V_{\rm ISET}$ , thus adjusting the LED current to a lower or higher value.

Figure 26: Adjusting LED current with an external voltage source

Equation 5:

$$i_{ISET} = \frac{V_{ISET}}{R_{ISET}} - \left[ \frac{VDAC - V_{ISET}}{R2} \right]$$

where  $V_{ISET}$  is the ISET pin voltage (typically 1.0 V), and VDAC is the DAC output voltage.

When VDAC is higher than 1.00 V, the LED current is reduced. When VDAC is lower than 1.00 V, the LED current is increased.

Some common applications for the above scheme include:

- LED binning

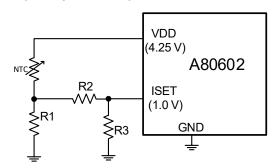

- Thermal fold-back using external NTC (negative temperature coefficient) thermistor

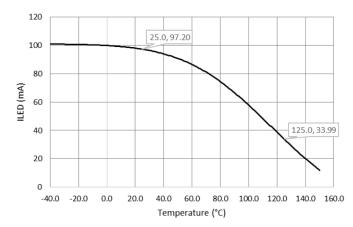

In the following application example, the thermistor used is NTC-S0805E3684JXT (680 k $\Omega$  @ 25°C). R1 = 336 k $\Omega$ , R2 = 20 k $\Omega$ , and R3 = 8.45 k $\Omega$ . The LED current per channel is reduced from 97 mA at 25°C to 34 mA at 125°C.

Figure 27: Thermal foldback of LED current using NTC thermistor

ILED VS Temperature with NTC Circuit

Figure 28: LED current varies with temperature when using thermistor NTCS0805E3684JXT for thermal foldback

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

#### **VDD**

The VDD pin provides regulated bias supply for internal circuits. Connect a  $C_{VDD}$  capacitor with a value of 1  $\mu F$  or greater to this pin. The internal LDO can deliver up to 2 mA of current with a typical VDD voltage of about 4.25 V. This allows it to serve as the pull up voltage for FAULT pin.

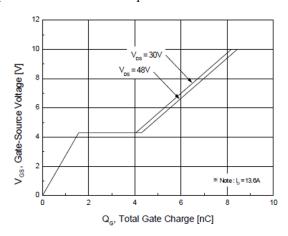

#### **VDRV**

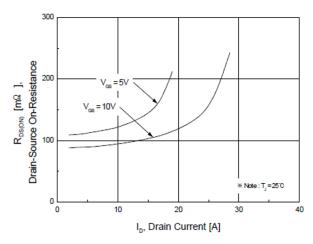

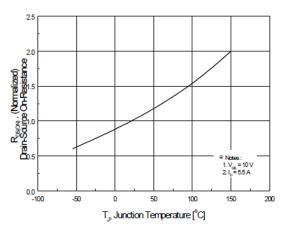

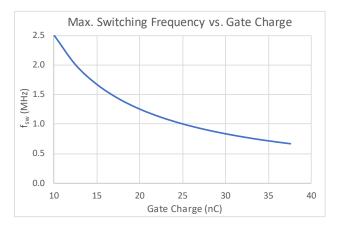

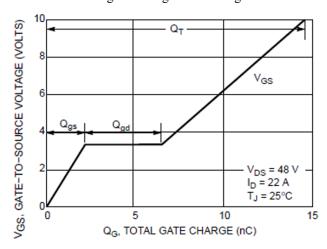

The VDRV pin provides a regulated gate driver supply for external boost power MOSFET. Connect a  $C_{VDRV}$  capacitor with a typical value of 2.2  $\mu F$  to this pin. The gate driver can deliver up to 2 A of peak sink and source current, with a typical  $V_{DRV}$  voltage of 6.5 V. However, its average output current is limited to approximately 36 mA. Note that average gate driver current is:

Equation 6:

$$i_{VDRV} = f_{SW} \times Q_{G}$$

where  $f_{SW}$  is the switching frequency and  $Q_G$  is the total gate charge of the power MOSFET for  $V_{GS} = 0$  to 6.5 V.

At higher switching frequency, it is important to select a power MOSFET with low  $Q_G$  to limit the average gate driver current. Refer to the appendix section for details on MOSFET selection.

#### Shutdown

If the EN/PWM pin is pulled low for longer than  $t_{\rm EN(OFF)}$  (~16 ms), the A80602 enters shutdown (sleep mode). The next time the EN/PWM pin goes high, all internal fault registers are cleared. The IC needs to go through a complete soft start process after PWM goes high.

Figure 29: After EN/PWM (Yellow) goes Low for ~16 ms, the IC completely shuts down so both VDD (Blue) and COMP (Red) decay.

#### FAULT DETECTION AND PROTECTION

#### **FAULT Status**

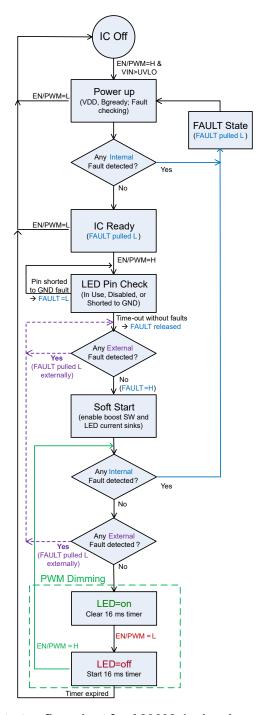

The FAULT pin is an open-drain output that is pulled low when a fault occurs. A pull-up resistor (typically around  $10~k\Omega$ ) is required between this pin and desired logic level voltage (typically 3.3 to 5 V). Multiple devices with open-drain FAULT pins can be connected in parallel to form a wired-AND configuration. This way, when any device reports a fault, the system FAULT signal is pulled low.

The A80602-1 (One-Out-All-Out option) has a bidirectional FAULT pin. This means the same pin also serves as an input to monitor the status of system FAULT signal. When the FAULT pin is pulled low externally for >8  $\rm f_{SW}$  cycles by another device, the A80602-1 disables its own boost switch and all LED current sinks in response. This feature is required in Master/Slave configuration, for example.

The following two simplified flow charts demonstrate the difference between A80602 (unidirectional FAULT pin) and A80602-1 (bidirectional FAULT pin).

Figure 30: Simplified A80602 Startup Flowchart

Figure 31: Simplified startup flow chart for A80602-1, showing responses to both Internal and External FAULT signals

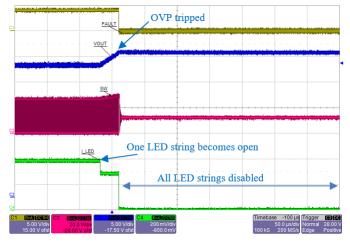

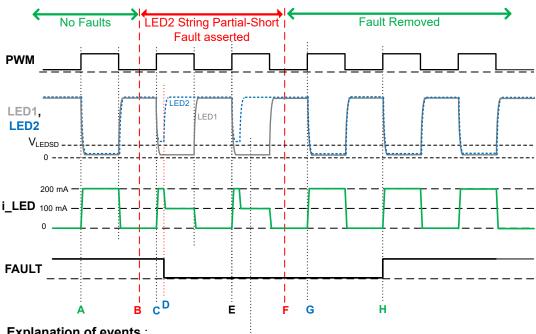

#### **LED String Partial-Short Detect**

All LED current sink pins (LED1 to LED6) are designed to withstand the maximum output voltage, as specified in the Absolute Maximum Ratings table. This prevents the IC from being damaged if  $V_{OUT}$  is directly applied to an LED pin due to an output connector short.

In case of direct-short or partial-shorted fault in any LED string during operation, the LED pin with voltage exceeding  $V_{\rm LEDSD}$  is removed from regulation. This prevents the IC from dissipating too much power due to large voltage drop across the LED current sink.

Figure 32: A80602 Normal startup sequence showing voltage at LED1 and LED2 pins.  $V_{IN}$  = 6 V, output = 8 × WLED in series, current = 6 × 100 mA

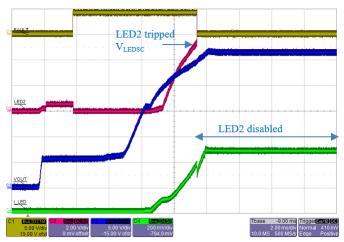

Figure 33: A80602 startup sequence when LED string#2 has a partialshort fault (6 × WLED instead of 8). As soon as LED2 pin rises above  $V_{LEDSC}$  (~5 V), the channel is disabled and FAULT = Low. All other channels continue as normal.

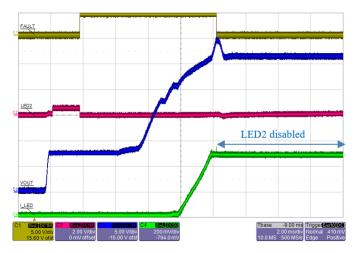

For A80602, the FAULT pin is pulled low in case any LED string is directly or partially shorted. The suspect LED string is disabled, while the rest of the LED strings continue to operate. FAULT pin is latched at low until it is reset by either EN = L or PWM = L for >16 ms

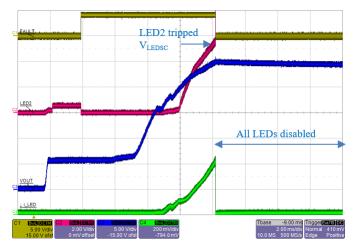

For A80602-1, all LED strings are turned off in case any LED string has detected a partial short. FAULT pin is latched at low until the IC is reset.

Figure 34: A80602-1 startup sequence when LED string#2 has a partial-short fault (6 × WLED instead of 8). As soon as LED2 pin rises above  $V_{LEDSD}$  (~5 V), all channels are disabled and FAULT = Low.

At least one LED pin must be at regulation voltage (below  $\sim 1.2 \text{ V}$ ) for the LED string partial-short detection to activate. In case all the LED pins are above regulation voltage (this could happen when the input voltage rises too high for the LED strings), they continue to operate normally.

### High Power LED Driver with Pre-Emptive Boost for Ultra-High Dimming Ratio and Low Output Ripple

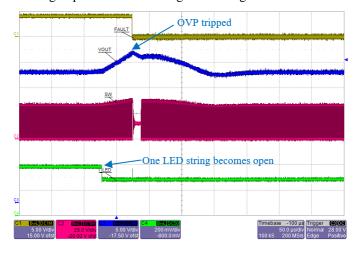

#### Overvoltage Protection

The A80602 offers a programmable output overvoltage protection (OVP). The OVP pin has a threshold level of 2.5 V typical. Overvoltage protection is tripped when current into this pin exceeds  $\sim\!150~\mu A$ . A resistor can be used to set the OVP threshold up to 40 V approximately. This is sufficient for driving 11 white LEDs in series.

The formula for calculating the OVP resistor is shown below:

Equation 7:

$$R_{OVP} = (V_{OVP} - V_{OVP(th)}) / i_{OVP(th)}$$

where  $V_{OVP}$  is the desired OVP threshold,  $V_{OVP(th)} = 2.5 \text{ V}$  typical,  $i_{OVP(th)} = 150 \mu\text{A}$  typical.

To determine the desired OVP threshold, take the maximum LED string voltage at cold and add ~10% margin on top of it.

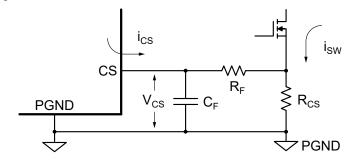

The OVP event is not a latched fault and, by itself, does not pull the FAULT pin to low. If the OVP condition occurs during a load dump, for example, the IC stops switching but does not shut down.